作者:mongcheng | 来源:互联网 | 2023-09-01 18:30

在实现过程中要注意很多问题。以2048点为例,根据理论值计算,计算一次2048点的IFFT的时间应为130us。在采用流水线的方式下,实部计算和虚部计算均采用两块RAM实现流水线。

上一篇文章介绍了FFT的硬件实现。 关于FFT的逆运算IFFT,实际上只要逆执行实现FFT的过程就可以了。

在实现的过程中必须注意许多问题。

和FFT一样,是效率的问题。 以2048点为例,根据理论值计算,一次计算2048点的IFFT的时间必须是130us。 采用流水线方式时,实部计算和虚部计算都采用2片RAM实现流水线。

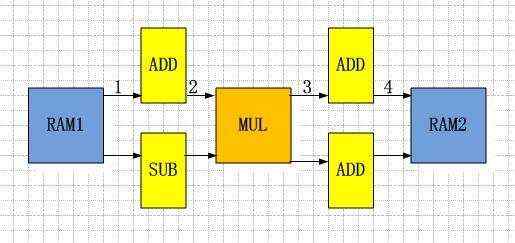

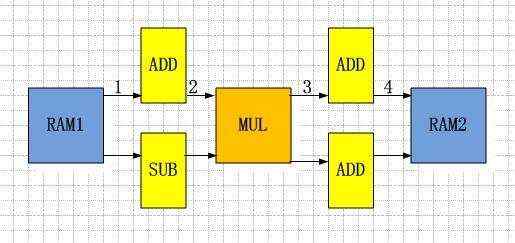

结构如上图所示。 在这种方式中,FPGA的片上RAM被消耗了很多。

为了节约RAM,可以采用一张RAM的流水线方式。 在实施过程中,需要注意RAM操作的读-写。 上一篇文章介绍了。 这种方式速度减半。

最节约的方法是使用控制器方式,但速度更低。 在此不做介绍。

上图所示的IFFT过程存在很多组合逻辑,定时还不够,所以应该在组合逻辑中加入寄存器来高速化。 但是,寄存器流水线的级数会影响读写两张RAM的切换,从而影响计算效率,因此值得在此进行讨论。

在设计中,RAM输出侧没有使用REG,所以应该在一个地方放入REG来提高速度。 否则,一处会发生计时违规,一处组合的逻辑延迟会变大。

两个地方和三个地方也是值得深思的地方。 请注意,从加法器的输出到乘法器的输入,以及从乘法器的输出到加法器的输入,都是大量的组合逻辑,不仅仅是功能模拟。 请务必在综合工具下进行综合,确认是否满足时机。 在实践中,两者都加入了REG。

是否在4个地方追加REG需要看综合结果。 实际分析表明,在4个地方添加REG会降低计算效率,导致读RAM和写RAM的时间来不及,这是基于自己设计的结果。

由于FFT计算过程使用乘法器,因此在IFFT中需要使用除法器。 要减少除法器使用的资源或将除法器改为其他逻辑实现,必须进行深入研究。

版权归勋爵精湛的技术,转载请注明出处

作者:勋爵萃科学技术ALIFPGA

原文地址:卿萃科技FPGA极客空间微信公众号

飞艇7码滚雪球技巧origin/pgc-image/1530586492695fcc048246f?from=pc">

两个地方和三个地方也是值得深思的地方。 请注意,从加法器的输出到乘法器的输入,以及从乘法器的输出到加法器的输入,都是大量的组合逻辑,不仅仅是功能模拟。 请务必在综合工具下进行综合,确认是否满足时机。 在实践中,两者都加入了REG。

是否在4个地方追加REG需要看综合结果。 实际分析表明,在4个地方添加REG会降低计算效率,导致读RAM和写RAM的时间来不及,这是基于自己设计的结果。

由于FFT计算过程使用乘法器,因此在IFFT中需要使用除法器。 要减少除法器使用的资源或将除法器改为其他逻辑实现,必须进行深入研究。

版权归勋爵精湛的技术,转载请注明出处

作者:勋爵萃科学技术ALIFPGA

原文地址:卿萃科技FPGA极客空间微信公众号